- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

2004 Microchip Technology Inc.

DS30491C-page 359

PIC18F6585/8585/6680/8680

24.4

Program Verification and

Code Protection

The overall structure of the code protection on the

PIC18 Flash devices differs significantly from other

PICmicro devices.

The user program memory is divided on binary bound-

aries into four blocks of 16 Kbytes each. The first block

is further divided into a boot block of 2048 bytes and a

second block (Block 0) of 14 Kbytes.

Each of the blocks has three code protection bits

associated with them. They are:

Code-Protect bit (CPn)

Write-Protect bit (WRTn)

External Block Table Read bit (EBTRn)

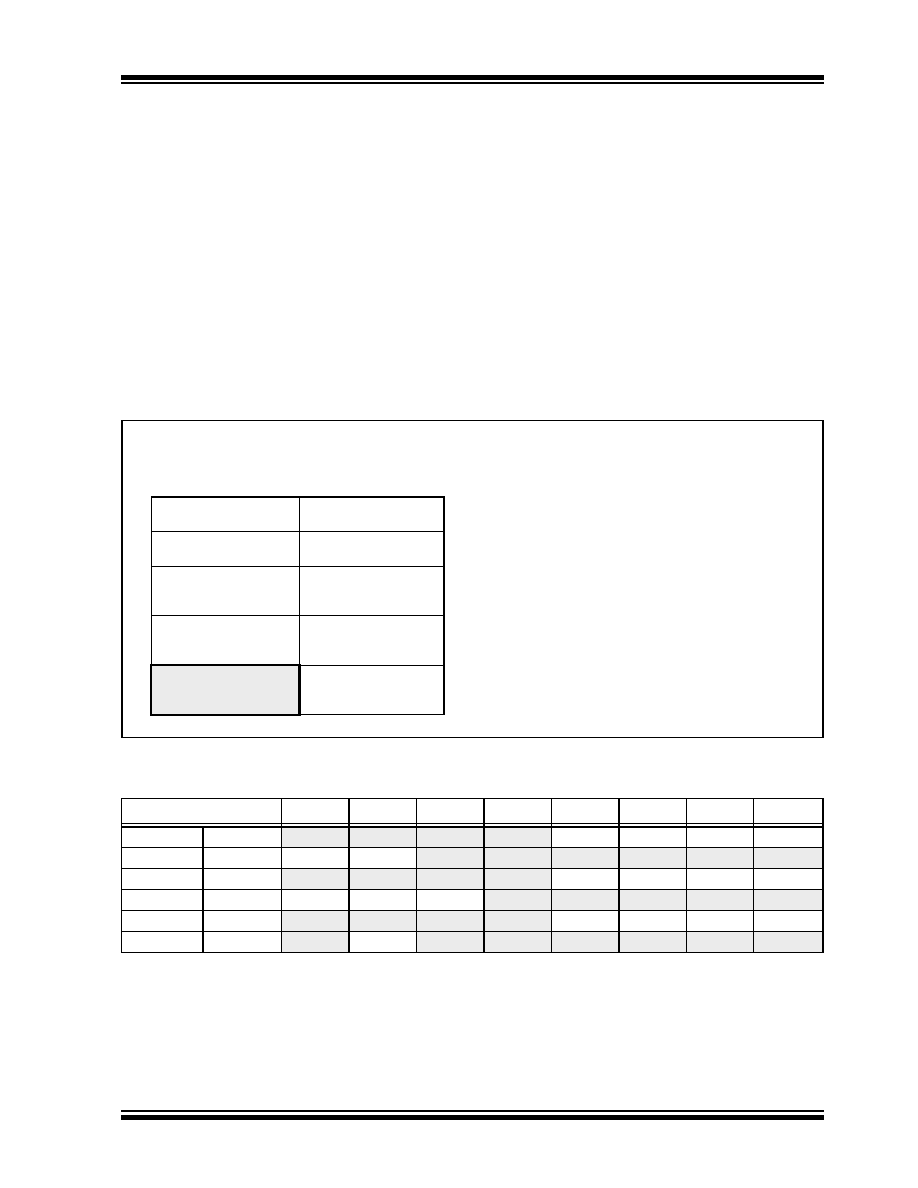

Figure 24-3 shows the program memory organization

for 48 and 64-Kbyte devices and the specific code

protection bit associated with each block. The actual

locations of the bits are summarized in Table 24-3.

FIGURE 24-3:

CODE-PROTECTED PROGRAM MEMORY FOR PIC18FXX8X DEVICES

TABLE 24-3:

SUMMARY OF CODE PROTECTION REGISTERS

MEMORY SIZE/DEVICE

Block Code Protection

Controlled By:

48 Kbytes

(PIC18FX585

64 Kbytes

(PIC18FX680)

Address

Range

Boot Block

000000h

0007FFh

CPB, WRTB, EBTRB

Block 0

000800h

003FFFh

CP0, WRT0, EBTR0

Block 1

004000h

007FFFh

CP1, WRT1, EBTR1

Block 2

008000h

00BFFFh

CP2, WRT2, EBTR2

Unimplemented Read ‘0’

Block 3

00C000h

00FFFFh

CP3, WRT3, EBTR3

File Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

300008h

CONFIG5L

—

—CP3(1)

CP2

CP1

CP0

300009h

CONFIG5H

CPD

CPB

—

30000Ah

CONFIG6L

—

—WRT3(1)

WRT2

WRT1

WRT0

30000Bh

CONFIG6H

WRTD

WRTB

WRTC

—

30000Ch

CONFIG7L

—

EBTR3(1)

EBTR2

EBTR1

EBTR0

30000Dh

CONFIG7H

—

EBTRB

—

Legend: Shaded cells are unimplemented.

Note 1:

Unimplemented in PIC18FX585 devices.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-2424-11

CONN FPC 24POS 0.5MM SMT

PIC18LF6585T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF6680T-I/PT

IC PIC MCU FLASH 32KX16 64TQFP

XF2J-2224-11

CONN FPC 22POS 0.5MM SMT

PIC18F6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18F4439-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2024-11

CONN FPC 20POS 0.5MM SMT

PIC16LF747-I/ML

IC PIC MCU FLASH 4KX14 44QFN

相关代理商/技术参数

PIC18F85J10-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J10-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-80 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-80

PIC18F85J10T-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048BRAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15T-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J50-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 3936byte RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT